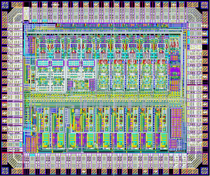

CareChip

Analog/Mixed-Signal Design and Verification Services

Carechip is experienced in the design and verification of analog/mixed-signal circuits such as analog video frontends, ADCs, DACs, LDOs, DC-DC converters and other power management blocks, including radiation-hardened circuits for space applications.

Services can include helping to create a spec., developing and providing a schematics database which can include test benches, and layout designing and performing physical verification.

Design and test of electronics circuits usign discrete components

Carechip has also a broad band experience in the design and test of electronic circuits using discrete components in areas such as:

- - Switching power supplies

- - Audio power amplifiers

- - Rf power amplifiers

- - Florescent electronic dimmers

- - Etc …

Contact us for more information.

Process Design Kits

Carechip can help in the development of all parts that constitute a Process Design Kit for the analog/mixed-signal flow of integrated circuits design: Cadence pcell libraries, technology files, and physical verification decks for Assura or Calibre for performing DRC (Design Rule Check), LVS (Layout vs. Schematic) and RCX (Parasitic Extraction).

Carechip's EDA collaborators have experience in the development of PDKs for CMOS processes, and have collaborated along time with foundries, providing feedback on issues found and suggestions for enhancement.

Software Development for EDA tools

Carechip's EDA collaborators are proefficient in programming and scripting languages such as C, Python, Tcl/Tk, Cadence Skill, which enables helping customers to add value in their existing design tools or providing customized off-the-shelf EDA tools of small-to-medium complexity.

The methodology used in software development follows the common practices in the industry, using version control and with thorough automated testing. All developed software is supported by detailed documentation.

Carechip collaborators have worked together over time with EDA players such as Cadence and Synopsys.

© CareChip,Lda. Website created by CareChip